Managing Electromagnetic Interference in PCB Design

Ensuring electromagnetic (EMI) resistance and EMC compliance is paramount in designing PCBs, and adherence to standards is critical in multiple applications. EMI/EMC regulations govern the emission and susceptibility of electromagnetic radiation from electronic devices, ensuring that they operate harmoniously in their intended environments without causing interference with other devices. This article delves into advanced strategies and considerations for achieving and maintaining compliance by addressing the nuanced challenges of PCB designers in specialized fields.

EMI and EMC Problems in Specific Contexts

EMI refers to the unintentional generation of electromagnetic noise by electronic devices, a noise that can disrupt the operation of nearby equipment. Conversely, electromagnetic compatibility (EMC) ensures that devices operate without being affected by external electromagnetic noise.

PCB designers must consider the various sources of electromagnetic noise, especially when working in domains with strict regulations. Noise can stem from ignition systems and electric motors (automotive), radar systems and communication equipment (military and aviation), and high-voltage power systems, and imaging equipment (medical). Ensuring ideal operation in noisy environments is crucial to the safety of operating personnel and others, because failures can result in catastrophic loss or compromised safety, potentially leading to injuries.

Distinguishing between lumped and distributed circuits is critical, because designers rarely encounter EMI problems when dealing with lumped circuits. In contrast, distributed circuits – those with a short rise time compared to their propagation time along signal lines – require careful planning to mitigate typical EMI problems, such as ringing and signal reflection. In analog circuits, the distinction happens based on the signal’s wavelength and the board material. Simulations are crucial in determining whether devices and transmission lines in a design have the potential to suffer from EMI. However, as a rule of thumb, designers can typically assume distributed transmission lines in almost all modern applications with short edge rise times and traces longer than a few millimeters.

Insufficient Return Paths as the Source of EMI Problems

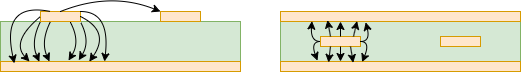

Many problems related to interference in PCB designs can be traced to insufficient current return paths. Current in a trace induces a magnetic field that radiates above and below the transmission line, and the return currents always follow the path of lowest inductance. Traces on the outer layers induce the field in the air surrounding the PCB, possibly inducing noise in nearby components and circuits. To mitigate these problems, designers can design short, low-impedance current return paths, for example, by employing striplines to route crucial distributed transmission lines between adequate return planes on the inner layers of the PCB stackup. Whether a transmission line is implemented as a stripline or microstrip trace, the trace must always run above a suitable reference plane or near a return line to minimize EMI problems.

Grounding Strategies for HF Transmission Lines

Ensuring that reference planes are not split underneath distributed transmission lines is equally significant in mitigating EMI; otherwise, designers could create unintentional antennas that radiate electric noise.

More importantly, HF twisted pairs and bus lines should always run above suitable current return paths to prevent crosstalk between the matched pairs or neighboring bus lines, which is especially important at high frequencies with narrower return current areas around the traces. For whatever reason, if designers cannot route such transmission lines above a suitable reference, they must place suitable reference traces between the bus lines, for example, to ensure adequate return paths between the distributed lines. While this may not be ideal, doing so reduces EMI between neighboring traces.

Ultimately, the goal is to reduce inductance between distributed lines and a suitable return current path while simultaneously increasing inductance between susceptible traces that should not interfere. Though using wider traces reduces inductance, moving transmission lines closer to a suitable reference has a far greater effect on mitigating EMI.

In that sense, designers should identify subcircuits in their design and create a layout that closely groups related components. Doing so helps them achieve short paths between the connected parts so that the transmission lines don’t become long enough to act as distributed lines. In those cases, designers can route the resulting lumped traces on the top layer above or close to a suitable reference to prevent losses caused by vias.

How Part Choices Affect EMI

Part selection may not be an inherent option to consider when reducing EMI in a circuit. However, similar to how return currents travel in traces, signals on IC pins also return using the path of lowest inductance. Thus, if designers can choose between similar devices or packages, they should pick one that distributes reference pins throughout the package layout so that signals of nearby pins have a greater chance of returning to a suitable reference pin instead of coupling back into a different neighboring one.

.png)

Subcircuit Placement and Isolated Ground Planes

Designers should identify subcircuits based on various aspects, such as analog/digital, voltages, and frequencies. Within those groups, connections should be kept at minimum lengths for ideal EMI properties. However, splitting ground planes within those areas is usually recommended only if there's a good reason to do so. If the aim is to mitigate noise propagating from one subcircuit group to another, splitting only the power planes generally yields more favorable outcomes. Similarly, designers should not run wires on ground layers, especially when working with susceptible analog signals. Similarly, employing zero-ohm resistors in those cases is advisable only in low-frequency circuits.

Instead of splitting ground planes between subcircuits, designers should aim for physical separation of the subcircuits on the PCB. As a rule of thumb, the separation between subcircuits should be about 20x the distance of the traces to their current return path to ensure ample spacing for the return currents of all subgroups.

How Vias Influence EMI

Considering EMI, coupling a transmission line from one side of a reference plane to the other using only a single via is no cause of concern, as its magnetic field couples over to the other side of the same plane through the via. Suppose a trace needs to change layers across different reference planes. In that case, designers should place an additional via connecting the two reference planes next to the signal via to provide a well-defined low-impedance return path and minimize field spread and EMI. Sensitive analog circuits may require the use of multiple reference vias around the signal via to create a field-containing barrier.

Because this approach may not be practical for dense PCB layouts, designers could group multiple signal vias of the same subcircuit and surround them with several reference vias to contain the magnetic field. Moving a signal line from a reference plane across a power plane often requires adding a capacitor to control low-frequency noise. High-frequency noise can be mitigated by closely bringing the reference and power planes together in the stackup, ideally within 8 mils. Finally, stitching vias can help prevent EMI in high-frequency analog circuits.

The Role of Physical Shielding

Metal enclosures around groups of components or an entire electronic device keep the circuit’s magnetic fields inside the unit and shield it against external influences by acting as a Faraday cage. However, connecting the reference plane to the chassis doesn’t automatically improve EMI resistance, and the coupling must be well-designed so as not to have a converse effect and exacerbate EMI problems.

Conclusion

Managing electromagnetic interference (EMI) is critical to PCB design. Engineers must pay attention to current return paths, utilizing short, low-impedance paths and optimizing trace routing, particularly for distributed transmission lines. Strategies such as using striplines, running twisted pairs and bus lines above suitable return paths, and physically separating subcircuits on the PCB all help to minimize EMI.

Part selection can significantly affect EMI, and the layout of reference pins within IC packages affects signal return paths. Identifying subcircuits based on analog/digital, voltage, and frequency aspects is essential, and connections should be kept at minimum lengths within groups. Avoid splitting ground planes within subcircuits, and split power planes only when necessary to mitigate noise.

When coupling transmission lines across reference planes, designers should use additional vias for a well-defined low-impedance return path and consider multiple reference vias for sensitive analog circuits. Metal cases act as Faraday cages, containing magnetic fields within the device, but connecting the reference plane to the chassis requires careful design to avoid exacerbating EMI problems.

Overall, designers should physically separate subcircuits, use proper grounding techniques, and optimize transmission line routing to minimize EMI. In addition, strategic part selection and thoughtful layout considerations contribute to achieving and maintaining EMC compliance in PCB designs.